- 您现在的位置:买卖IC网 > Sheet目录342 > MB85RS64PNF-G-JNE1 (Fujitsu Semiconductor America Inc)IC FRAM 64KBIT 20MHZ 8SOP

�� �

�

MB85RS64A�

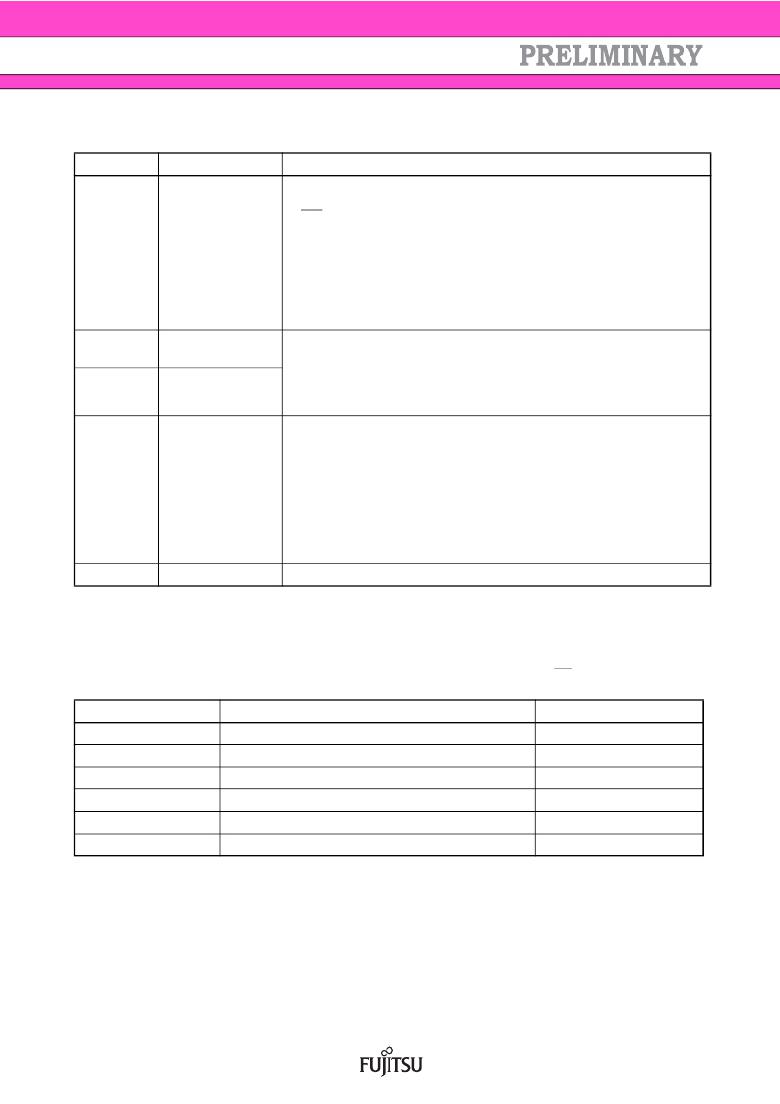

�■� STATUS� REGISTER�

�Bit� No.�

�7�

�6� to� 4�

�3�

�2�

�1�

�0�

�Bit� Name�

�WPEN�

�?�

�BP1�

�BP0�

�WEL�

�0�

�Function�

�Status� Register� Write� Protect�

�This� is� a� bit� composed� of� nonvolatile� memories� (FRAM).� WPEN� is� related�

�to� WP� input� to� protect� writing� to� a� status� register� (refer� to� “� ■� WRITING�

�PROTECT”).� Writing� with� the� WRSR� command� and� reading� with� the�

�RDSR� command� are� possible.�

�Not� Used� Bits�

�These� are� bits� composed� of� nonvolatile� memories,� writing� with� the� WRSR�

�command� is� possible,� and� “000”� is� written� before� shipment.� These� bits� are�

�not� used� but� they� are� read� with� the� RDSR� command.�

�Block� Protect�

�This� is� a� bit� composed� of� nonvolatile� memory� (FRAM).� This� defines� block�

�size� for� writing� protect� with� the� WRITE� command� (refer� to� “� ■� BLOCK�

�PROTECT”).� Writing� with� the� WRSR� command� and� reading� with� the�

�RDSR� command� are� possible.�

�Write� Enable� Latch�

�This� indicates� FRAM� memory� and� status� register� are� writable.� The� WREN�

�command� is� for� setting,� and� the� WRDI� command� is� for� resetting.� With� the�

�RDSR� command,� reading� is� possible� but� writing� is� not� possible� with� the�

�WRSR� command.� WEL� is� reset� after� the� following� operations.�

�The� time� when� power� is� up.�

�The� time� when� the� WRDI� command� is� input.�

�The� time� when� the� WRSR� command� is� input.�

�The� time� when� the� WRITE� command� is� input.�

�This� is� a� bit� fixed� to� “0”.�

�■� OP-CODE�

�MB85RS64A� accepts� 6� kinds� of� command� specified� in� op-code.� Op-code� is� a� code� composed� of� 8� bits�

�shown� in� the� table� below.� Do� not� input� invalid� codes� other� than� those� codes.� If� CS� is� risen� while� inputting�

�op-code,� the� command� are� not� performed.�

�Name� Description� Op-code�

�6�

�WREN�

�WRDI�

�RDSR�

�WRSR�

�READ�

�WRITE�

�Set� Write� Enable� Latch�

�Reset� Write� Enable� Latch�

�Read� Status� Register�

�Write� Status� Register�

�Read� Memory� Code�

�Write� Memory� Code�

�0000� 0110� B�

�0000� 0100� B�

�0000� 0101� B�

�0000� 0001� B�

�0000� 0011� B�

�0000� 0010� B�

�DS501-00009-0v01-E�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MC10SX1130DR2

IC LED DRIVER LINEAR 16-SOIC

MC33152DG

IC DRIVER MOSFET DUAL HS 8SOIC

MC33153PG

IC DRIVER GATE SINGLE IGBT 8DIP

MC34151DG

IC MOSFET DRIVER DUAL HS 8SOIC

MC34844EP

IC LED DVR BACKLIGHT 10CH 32QFN

MC34845AEPR2

IC LED DVR BACKLIGHT 6CH 24QFN

MC34845BEPR2

IC LED DVR BACKLIGHT 6CH 24QFN

MC34848EPR2

IC LED DVR BACKLIGHT 8CH 48QFN

相关代理商/技术参数

MB85RS64PNF-G-JNERE1

制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:"MB85RS64PNF-G-JNERE1",64KSPI,FRAM 制造商:FUJITSU 功能描述:64Kbit SPI,FRAM 制造商:FUJITSU 功能描述:SPI,64K FRAM

MB85RS64V

制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:64 K (8 K ?? 8) ?????????SPI

MB85RS64VPNF-ES-JNE1

制造商:FUJITSU 功能描述:

MB85RS64VPNF-G-JNE1

制造商:FUJITSU 功能描述:

MB85RS64VPNF-G-JNERE1

制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:IC FRAM 64KBIT 20MHZ 8SOP 制造商:FUJITSU 功能描述:"MB85RS64VPNF-G-JNERE1",64KSPI,FRAM 制造商:FUJITSU 功能描述:64Kbit SPI,FRAM 制造商:FUJITSU 功能描述:SPI,64K FRAM

MB86

功能描述:ACCY MOUNT BMM 3/4 58A RoHS:是 类别:RF/IF 和 RFID >> RF配件 系列:* 标准包装:1 系列:*

MB86029

制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:TV/VCR D/A Converter (3 ch, 8 bit)

MB86040

制造商:FUJITSU 制造商全称:Fujitsu Component Limited. 功能描述:CMOS PIPELINED DIVIDER WITH 10-BIT DIVIDEND, 8BIT DIVISOR, AND 10-BIT QUOTIENT